TIAGO COGUMBREIRO, Rice University, USA RAYMOND HU, Imperial College London, UK FRANCISCO MARTINS, LASIGE and University of the Azores, Portugal NOBUKO YOSHIDA, Imperial College London, UK

We present Armus, a verification tool for dynamically detecting or avoiding barrier deadlocks. The core design of Armus is based on phasers, a generalisation of barriers that supports split-phase synchronisation, dynamic membership, and optional-waits. This allows Armus to handle the key barrier synchronisation patterns found in modern languages and libraries. We implement Armus for X10 and Java, giving the first sound and complete barrier deadlock verification tools in these settings.

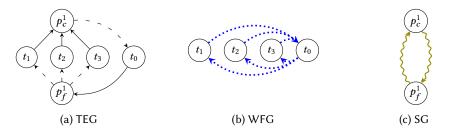

Armus introduces a novel event-based graph model of barrier concurrency constraints that distinguishes task-event and event-task dependencies. Decoupling these two kinds of dependencies facilitates the verification of distributed barriers with dynamic membership, a challenging feature of X10. Our base graph representation can also be dynamically switched between a task-to-task model, Wait-for Graph (WFG), and an event-to-event model, State Graph (SG), to improve the scalability of the analysis.

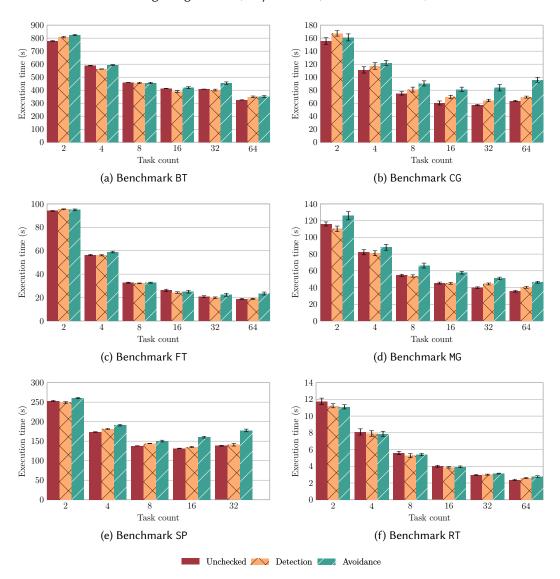

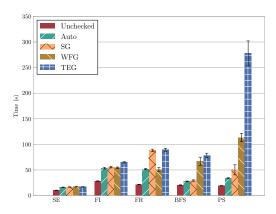

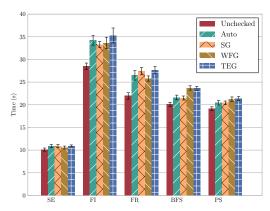

Formally, we show that the verification is sound and complete with respect to the occurrence of deadlock in our core phaser language; and that switching graph representations preserves the soundness and completeness properties. These results are machine checked with the Coq proof assistant. Practically, we evaluate the runtime overhead of our implementations using three benchmark suites in local and distributed scenarios. Regarding deadlock detection, distributed scenarios show negligible overheads and local scenarios show overheads below 1.15×. Deadlock avoidance is more demanding, and highlights the potential gains from dynamic graph selection. In one benchmark scenario, the runtime overheads vary from: 1.8× for dynamic selection, 2.6× for SG-static selection, and 5.9× for WFG-static selection.

# $\label{eq:ccs} \mbox{CCS Concepts:} \bullet \mbox{Software and its engineering} \rightarrow \mbox{Deadlocks}; \mbox{Software verification}; \mbox{Dynamic analysis}; \mbox{Concurrent programming structures}; \mbox{Semantics}; \mbox{}$

Additional Key Words and Phrases: barrier synchronisation, phasers, deadlock detection, deadlock avoidance, X10, Java

#### **ACM Reference Format:**

Tiago Cogumbreiro, Raymond Hu, Francisco Martins, and Nobuko Yoshida. 2018. Dynamic Deadlock Verification for General Barrier Synchronisation. *ACM Trans. Program. Lang. Syst.* 1, 1, Article 1 (January 2018), 38 pages. https://doi.org/10.1145/nnnnnnnnnn

Authors' addresses: Tiago Cogumbreiro, Rice University, Department of Computer Science, Houston, TX, USA, cogumbreiro@rice.edu; Raymond Hu, Imperial College London, Department of Computing, London, UK, raymond.hu05@imperial.ac.uk; Francisco Martins, LASIGE and University of the Azores, Faculty of Sciences and Technology, Ponta Delgada, Portugal, fmartins@acm.org; Nobuko Yoshida, Imperial College London, Department of Computing, London, UK, n.yoshida@imperial.ac.uk.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.org.

© 2018 Association for Computing Machinery.

0164-0925/2018/1-ART1 \$15.00

https://doi.org/10.1145/nnnnnnnnnnn

ACM Transactions on Programming Languages and Systems, Vol. 1, No. 1, Article 1. Publication date: January 2018.

#### **1 INTRODUCTION**

*Dynamic verification of barrier deadlocks.* The rise of multicore processors and networked clusters has pushed mainstream programming languages to incorporate various concurrency features, an important class of which are *barriers* and their related mechanisms. The basic functionality of a barrier is to designate a point in the execution of a group of tasks at which each task is blocked until all have reached the barrier. Java 5–8 and .NET 4, for example, introduced several standard APIs that provide barriers explicitly or are built on top of barriers: latches, cyclic barriers, fork/join, futures, and streams. Recent languages for parallel programming have also been designed with more advanced abstractions as first-class language features, such as *clocks* in X10 [10] and *phasers* in Habanero-Java (HJ) [8], that are more expressive than basic barriers.

As with many other concurrency mechanisms, *deadlocks*—in which two or more tasks blocked on distinct barriers are waiting (perhaps indirectly) for each other—are one of the primary errors arising in barrier programs. Historically, the approach to counter barrier deadlocks has been to restrict the permitted barrier synchronisation patterns such that programs are barrier-deadlock free by construction; *e.g.*, OpenMP<sup>1</sup> restricts barrier composition to syntactic nesting. Unfortunately, to date there are no available tools for comprehensive verification of barrier-deadlocks in X10 or HJ, nor for standard libraries such as the Java Phaser<sup>2</sup> and the .NET Barrier [44] APIs.

Two key issues make barrier-deadlock verification challenging in these recent languages and systems. The first is that barriers may be created dynamically and communicated among tasks as values, referred to as *first-class barriers* [67]. Due to the difficulty of statically analysing the usage of first-class barriers *precisely* (*e.g.*, due to aliases and non-determinism), the state-of-the-art in barrier-deadlock verification is based on *dynamic* techniques that monitor program execution at run-time. (Existing tools for static verification are limited to simpler systems where barriers permit only global, *i.e.*, system-wide, synchronisations; see Section 8.) The second is that, in contrast to the conservative restrictions in earlier systems, the richer barrier features in recent languages are motivated by expressiveness at the cost of making deadlock verification, including dynamic approaches, more complicated. One of the key features supported in Java, .NET, X10, and HJ, but not handled by any existing barrier-deadlock verification tool, is *dynamic membership* [53], which allows the group of tasks participating in synchronisations on a barrier to change during execution.

The state-of-the-art in dynamic barrier-deadlock verification is based on the well-established concept of *Wait-For Graph* (WFG) and has been developed for MPI<sup>3</sup> (*e.g.*, the MUST error detection tool [32, 34]) and UPC<sup>4</sup> [57]. A WFG [40] is a graph model of the control flow dependencies between tasks. Applied to barriers, the WFG nodes represent tasks, and a directed edge from a task *t* to task *t'* signifies that *t* is blocked on a barrier, waiting for *t'* to reach the barrier. WFG-based approaches typically work by maintaining an abstract representation of the concurrency constraints in a system, from which the WFG can be derived and deadlock detection performed as a suitable graph analysis, such as checking for circular dependencies.

Existing WFG-based tools, such as MUST, offer precise deadlock detection in systems featuring multiple barriers, but suffer from limitations in the presence of more advanced barrier features. One is that they are designed on the assumption of static barrier membership (as is the case for MPI barriers). Naive extension to dynamic membership faces the challenges of maintaining the membership status of barriers consistently (since barrier synchronisations and (de)registration operations occur concurrently) and efficiently (*e.g.*, w.r.t. the overheads of any additional state

<sup>&</sup>lt;sup>1</sup>http://openmp.org/

<sup>&</sup>lt;sup>2</sup>https://docs.oracle.com/javase/8/docs/api/java/util/concurrent/Phaser.html

<sup>&</sup>lt;sup>3</sup>http://mpi-forum.org/

<sup>&</sup>lt;sup>4</sup>https://upc-lang.org/

synchronisations used for consistency). These issues are exacerbated by *distributed barriers*, a key design point of X10.

Another limitation is committing exclusively to the WFG model. The WFG originates from a distributed databases setting [40] involving a fixed number of tasks and dynamic resource creation. The WFG was thus optimised for concurrency constraints between fewer tasks and more resources, which is often not the case in more advanced barrier programs with dynamic task spawning and barrier creation, as possible in X10 and Java. Its counterpart, the *State Graph* (SG) [12] favours scenarios with more tasks than barriers. In general, however, we may expect that the most suitable model cannot be predicted a priori, and that the situation may change as execution proceeds. Committing to a specific graph model may thus hinder the scalability of dynamic deadlock verification.

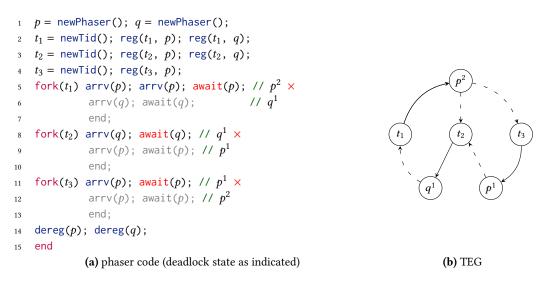

*Armus.* This paper presents Armus, a dynamic verification framework for general barrier deadlocks based on *phasers*. A phaser is a generalisation of the concept of barrier that allows tasks to *selectively* wait on barrier steps, thus permitting any task to progress to an arbitrary future step (*i.e., phase*) independently of its peers. (Section 2.3 will give more a detailed overview.) Phasers were originally developed in Habanero-Java (HJ) [8, 62] as an extension of X10 clocks, one of the primary motivations being to support asynchronous producer/consumer patterns. Armus is the first framework to support sound and complete deadlock verification for phasers. The key elements of Armus are as follows.

- We formalise the operations of a core concurrent language with phasers that subsumes the barrier facilities of X10, HJ, and the standard Java/.NET Barrier APIs, including dynamic membership. We characterise phaser deadlocks in our language in terms of dependencies between tasks and *synchronisation events* on phasers.

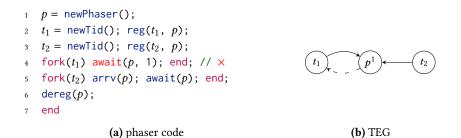

- On the basis of the above, we introduce a new model for general barrier-deadlock verification, the *Task-Event Graph* (TEG). We show that deadlock verification by TEG cycle detection is sound and complete with respect to our characterisation of phaser deadlock.

- We show that a WFG and an SG can be readily derived from a TEG, such that all three models are equivalent w.r.t. the existence of cycles. This promotes a technique to improve the scalability of the graph-based verification, by automatically and dynamically switching between models.

- We implement Armus as Armus-X10 and JArmus. Armus-X10 is the first sound and complete deadlock verification tool for native X10 programs using clocks and finish-barriers. We show how the design of Armus lends well to *distributed barriers*, as implemented in Armus-X10. JArmus is the corresponding tool for Java programs using the Phaser API (and related barrier APIs) extended with one additional method for explicitly registering tasks with phasers.

Armus proposes the TEG model, with its notion of barrier synchronisation events, firstly as a means to capture the richer concurrency dependencies of phaser systems, in comparison to standard barriers. Modelling explicit synchronisation events arises naturally from the fact that tasks waiting on a given phaser may actually be waiting at arbitrarily different *phases*. The insight of Armus is to interpret the act of waiting on a particular phase as observing a timestamp, in a similar spirit to Lamport's logical clocks [41], by which we infer dependencies between a task and not only its current phase event (as with basic barriers), but also all future events.

Secondly, the TEG is an effective model for treating dynamic membership. Generating traditional wait-for dependencies directly between tasks requires synchronised bookkeeping between the blocking status and barrier membership of every such pair of tasks. The commonplace technique for building a WFG is to range over every blocked task and then query the blocked operation for its missing participants. Note, however, that for a barrier with dynamic membership, the complete

Tiago Cogumbreiro, Raymond Hu, Francisco Martins, and Nobuko Yoshida

set of participants can only be known at the end of synchronisation. Armus avoids this issue by decomposing the dependencies into separate relations between tasks and events—a dependency from a blocked task to an event can be asserted *independently* of the membership of the relevant phaser. This in turn facilitates the application of Armus to distributed barriers: instead of needing to synchronise the status of two potentially *remote* tasks for each wait-for dependency, Armus allows the global view of the system to be built from the *local* status of each blocked task (the event being observed, and the phaser memberships of the task) and the monotonic causal ordering of events.

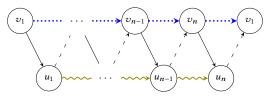

Dynamically selecting between graph models for deadlock detection, based on the monitored ratio of tasks to barriers, is a novel technique of Armus. The difference on the size of the graph can be dramatic. For instance, in an X10 benchmark PS (see Section 7.3),<sup>5</sup> the average edge count for the WFG model is 789 and the SG is 7, while the average using dynamic model selection is 6 (Table 3); and the average execution times, for deadlock avoidance, are 113s for WFG, 50s for SG, and 34s for dynamic model selection (Figure 9). In all cases of our benchmarks, the automatic model selection performs at least as well (*i.e.*, with negligible overheads) as manually selecting the best fixed model.

Outline. This article revises and extends an earlier version of this work [13] with new material and full proofs of results. Firstly, we include a new section with a comprehensive summary of barrier features found in practice and their deadlock characteristics. Regarding our core phaser language, first proposed in the earlier work, we add primitives for awaiting on a phaser at an arbitrary phase, and awaiting on a phaser by an unregistered task; these are needed to model the full functionality of phasers in HJ. Based on the extended language, we make significant updates to the core definitions of phaser deadlocks and dependency relations both in terminology and technical details. The definitions of Task-Event Graph construction, and Wait-For/State Graph contraction, are also revised technically. Regarding the properties of Armus, we develop new proofs of the soundness and completeness of the verification, and graph model equivalence, according to the updated definitions. We highlight that all definitions and proofs in this paper have been formalised and machine-checked in Coq, which is new to this article. Compared to the earlier work, we offer more detailed explanations and extended discussion of the practical methodology and implementations. The performance evaluation is also updated, including new benchmarks to evaluate deadlock verification using the TEG directly, in addition to the WFG/SG. Throughout the paper, we have extended the discussions and included many new examples with detailed explanations. Lastly, we have updated the related work with recent publications.

The structure of this article is as follows.

**Section 2** firstly covers the background to this work. We give barrier programming examples in X10, and summarise a range of barrier programming features found in practice and their deadlock characteristics. Secondly, we explain the concept of phasers, and outline the phaser-based approach of Armus to deadlock verification for general barrier synchronisations.

**Section 3** defines the core concurrent language with phasers used by Armus to capture all of the surveyed barrier programming features. We define the notions of global and local phaser deadlocks for Armus systems in terms of dependencies between tasks and synchronisation events.

**Section 4** presents the deadlock verification methodology of Armus. We define the derivation of a TEG model from Armus system states, and the transformation of a TEG to the associated WFG or SG.

<sup>&</sup>lt;sup>5</sup>http://www.cs.columbia.edu/~martha/courses/4130/au13/

```

Listing 1. Coordinating parallel tasks using cyclic and join barriers in X10.

```

```

// Pre: "a" is an array length I+1, initialised to: 0, 0, 0, ..., I

1

val c = Clock.make();

// Cyclic barrier

2

// Join barrier

finish {

3

for (i in 1..(I-1))

// Spawn I-1 child tasks..

4

async clocked(c) {

5

for (j in 1...J) { // ...that loop (together) J times

6

val l = a(i-1);

7

val r = a(i+1);

8

// Read step on the clock (cyclic synchronisation)

c.advance();

9

a(i) = (1+r)/2;

10

// Write step on the clock (cyclic synchronisation)

c.advance();

11

12

}

}

13

} // Wait for all child tasks to terminate (join synchronisation)

14

// Result: "a" holds values: 0, 1, 2, ..., I

15

```

**Section 5** shows the main results of Armus: that a TEG and the associated WFG and SG are equivalent w.r.t. the presence of cycles, and that cycle detection in a TEG derived from a system state is sound and complete w.r.t. the occurrence of deadlocks in the system.

**Section 6** presents the implementation of Armus for X10 (Armus-X10) and Java (JArmus). We discuss the application of Armus to distributed barriers, implemented in Armus-X10.

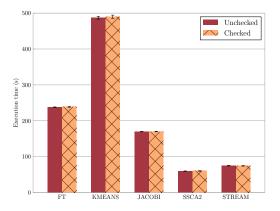

**Section 7** performs an extensive performance evaluation of Armus in Java and X10, using the NAS Parallel Benchmark, the Java Grande Forum Benchmark suite, and the HPC Challenge benchmark suite. Overall, the worst-case runtime-factor for deadlock detection is  $1.21\times$ , and is often not statistically significant, *e.g.*, in distributed benchmarks.

Section 8 discusses related work and Section 9 concludes.

The Armus project Web page<sup>6</sup> includes the full Coq implementation of the definitions and proofs, full source code for the Armus-X10 and JArmus implementations, and the benchmark scripts and data.

# 2 BARRIER-BASED PARALLEL PROGRAMMING AND DEADLOCKS

# 2.1 Cyclic and Join Barriers in X10

We start with an introductory *deadlocked* parallel program that uses barriers, written in X10. Listing 1 implements a simple parallel iterative averaging algorithm [19, 63] that takes a onedimensional array of I+1 numbers, for I>1, initialised to 0 except for the last element, which is set to I. The algorithm converges on the sequence of natural numbers from 0 through I by repeatedly updating, in parallel, each of the elements (except first and last) to an average of its neighbours. This example features two kinds of barriers: *cyclic* barriers, for recurrent synchronisation between a set of ongoing tasks, and *join* barriers, for synchronisation on the termination of a set of tasks.

A parallel task is spawned by the async statement (Line 5) inside the outer for-loop for each index 1 through I-1. A cyclic barrier, represented by the *clock* created and assigned to c (an immutable val) on Line 2, is used to coordinate these tasks. Each child task is *registered* (clocked) to the clock; the parent task is implicitly registered on clock creation. The work performed by each

<sup>&</sup>lt;sup>6</sup>https://bitbucket.org/cogumbreiro/armus/wiki/TOPLAS17

|                             | UPC          | MPI          | Java         | .NET         | X10          | НJ           | (Armus)      |

|-----------------------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| Group synchronisation       | ×            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Split-phase synchronisation | $\checkmark$ |

| Dynamic membership          | ×            | ×            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Async. producer-consumer    | ×            | ×            | ×            | ×            | ×            | $\checkmark$ | $\checkmark$ |

Table 1. Barrier synchronisation features supported in various languages.

task in the inner for-loop is split into read and write steps, delimited by the advance operations on c. A barrier synchronisation is performed by calling advance: the calling task is blocked until *every* task registered to the clock has called advance. The first advance (Line 9) thus ensures every task i completes the read step of the current j-th iteration, reading the a(i-1) and a(i+1) values, before any can proceed to the write step. The second advance similarly ensures every task has finished the current write step, writing the average of the read values to a(i), before any can proceed to the (j+1)-th iteration.

The finish statement applies a join barrier that blocks the executing task (the parent task) at the end of the finish (Line 14) until all nested tasks (the I-1 child tasks) have terminated.

Deadlock due to advanced barrier features. Certain barrier systems are restricted by design to ensure deadlock-freedom (see Section 2.2). By contrast, incorrect use of more advanced barrier features supported in modern systems such as X10 may give rise to subtle deadlock situations. The above example demonstrates a deadlock related to group synchronisation, where different, but not necessarily disjoint, groups of tasks are registered to separate barriers, and dynamic membership of tasks to barrier groups.

The deadlock arises from every child task being blocked on its first advance call (Line 9) because the parent task never performs the corresponding advance. Instead, the parent task is blocked on the finish, waiting for the child tasks to terminate, establishing a cyclic dependency between the parent and each child task.

For both the clock and finish barriers, each child task is *dynamically* registered at some execution point after the barrier is created: the clock and finish barriers are created on Lines 2 and 3, and the child tasks are spawned and registered later, one by one, in each iteration of Line 5 by the parent task. Tasks may similarly be dynamically *deregistered* from a barrier. The natural fix for the above deadlock is to have the parent task perform the deregistration operation on the clock, c.drop(), between Lines 13 and 14. Then the resulting synchronisation groups will be such that all tasks are registered to the finish barrier, but only the child tasks are registered to the clock.

Note: it would be incorrect for the parent task to drop its clock membership prior to spawning all the child tasks (or similarly, if X10 did not implicitly register the parent task on clock creation). This would avoid the deadlock, but also introduce a race condition between the collective iteration of the child tasks due to the concurrency between the running tasks and any remaining spawns by the parent.

# 2.2 An Overview of Barrier Synchronisation Features and Deadlock Errors

We give an overview of a range of key barrier synchronisation features, as supported by the languages and libraries in Table 1. We briefly discuss the purpose of each feature, and the implications for deadlock detection, with small examples. Table 2 summarises up front the support for deadlock verification currently available to programmers in each setting. Prior to Armus, there were no

|                                   | UPC          | MPI (MUST)                  | Java | .NET | X10 | НJ                        | Armus        |

|-----------------------------------|--------------|-----------------------------|------|------|-----|---------------------------|--------------|

| Barrier deadlock<br>verification? | $\checkmark$ | √ (for group<br>sync. only) | _    | _    | _   | sound (but<br>incomplete) | $\checkmark$ |

Table 2. Available support for (dynamic) deadlock verification with respect to the barrier features in Table 1. (' $\checkmark$ ' means both sound and complete; '-' means no support.)

comprehensive barrier deadlock detection facilities or tools, dynamic or otherwise, that supports all of the listed features.

The languages/libraries in Tables 1 and 2 are as follows. **UPC** refers to the barrier functionality of Berkeley Unified Parallel C.<sup>7</sup> **MPI** refers to the MPI\_Barrier and MPI\_IBarrier operations on an MPI communicator.<sup>8</sup> **X10** refers to clocks (whose functionality subsumes that of finish-barriers and SPMDBarrier). **HJ** (and **Armus**) refer to the functionality of *phasers*, explained later in Section 2.3. **Java** refers to the standard Phaser API,<sup>2</sup> which is a limited version of the general concept of phasers (see Section 6.4), but nevertheless subsumes the capabilities of other standard Java barrier libraries such as CyclicBarrier and CountDownLatch. **.NET** refers to the standard Barrier API,<sup>9</sup> which is the .NET counterpart of the Java Phaser.

*Group synchronisation.* Barrier programming in UPC is restricted to conducting "global" synchronisations, where every task in a system is implicitly a member of every barrier. A system that only involves such global barriers is deadlock-free if and only if all tasks synchronise on the same barriers in the same order: simply detecting that any two tasks are blocked on different barriers is sufficient to conclude a *global deadlock, i.e.*, that every task in the whole system is (or will become) stuck [57].

Group synchronisation, supported in every other case of Table 1, is the generalisation that permits an arbitrary subset of system tasks to be registered to a barrier. This introduces the notion of *local deadlocks*, where a subset of system tasks can never progress despite the progress of the system as a whole. The finer granularity of this feature is more expressive, but deadlock detection in turn requires checking for a more general form of circular control flow dependencies between multiple tasks transitively.

The standard approach in practice is to model the concurrency constraints of a system as a *Wait-For Graph* (WFG), in which circular dependencies manifest as graph cycles. When applied to barriers, the nodes of a WFG represent the tasks, and the edges represent the task-to-task *wait-for* relation induced by a task being blocked on a barrier that a co-member task has not yet reached. For MPI, the MUST tool includes sound and complete deadlock detection for barriers with group synchronisation (since every MPI communicator is an implicit barrier group) by a WFG approach [32, 34].

EXAMPLE 2.1. In Figure 1 (a), three tasks each synchronise on a different subset of two clocks out of three (a, b, and c). Once all three tasks are spawned, each barrier is synchronising on a different group of two tasks. The order in which each task advances its clocks establishes a circular dependency between all three tasks involving all three clocks, *i.e.*,  $t_1$  wait-for  $t_2$  via a,  $t_2$  wait-for  $t_3$  via b, and  $t_3$  wait-for  $t_1$  via c.

<sup>&</sup>lt;sup>7</sup>http://upc.lbl.gov/publications/upc-lang-spec-1.3.pdf (§ 6.6.1)

<sup>&</sup>lt;sup>8</sup>http://www.mpi-forum.org/docs/mpi-3.1/mpi31-report.pdf (§ 5.3)

<sup>&</sup>lt;sup>9</sup>https://msdn.microsoft.com/en-us/library/system.threading.barrier

|                                          | I                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                              | I                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| async clocked(a, c) { // $t_1$           | <pre>1 async clocked(a, b) {</pre>                                                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                                                                                                            | <pre>async clocked(a, b) {</pre>                                                                                                                                                                                                                                                                                                                                                                               |

| a.advance(); // ×                        | <sup>2</sup> if (condition) {                                                                                                                                                                                          | 2                                                                                                                                                                                                                                                                                                                                                                            | b.advance(); // ?                                                                                                                                                                                                                                                                                                                                                                                              |

| c.advance();                             | <pre>b.resume();</pre>                                                                                                                                                                                                 | 3                                                                                                                                                                                                                                                                                                                                                                            | }                                                                                                                                                                                                                                                                                                                                                                                                              |

| }                                        | 4   }                                                                                                                                                                                                                  | 4                                                                                                                                                                                                                                                                                                                                                                            | if (condition) {                                                                                                                                                                                                                                                                                                                                                                                               |

| async clocked(b, a) { // $t_2$           | 5   a.advance(); // ?                                                                                                                                                                                                  | 5                                                                                                                                                                                                                                                                                                                                                                            | b.drop();                                                                                                                                                                                                                                                                                                                                                                                                      |

| b.advance(); // ×                        | <pre>6 b.advance();</pre>                                                                                                                                                                                              | 6                                                                                                                                                                                                                                                                                                                                                                            | '<br>  }                                                                                                                                                                                                                                                                                                                                                                                                       |

| a.advance();                             | 7   }                                                                                                                                                                                                                  | 7                                                                                                                                                                                                                                                                                                                                                                            | a.advance(); // ?                                                                                                                                                                                                                                                                                                                                                                                              |

| }                                        | <pre>8   b.advance(); // ?</pre>                                                                                                                                                                                       | 8                                                                                                                                                                                                                                                                                                                                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                              |

| async clocked(c, b) { // $t_3$           | <pre>9 a.advance();</pre>                                                                                                                                                                                              | 9                                                                                                                                                                                                                                                                                                                                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                              |

| c.advance(); // ×                        | 10                                                                                                                                                                                                                     | 10                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                |

| <pre>b.advance();</pre>                  | 11 /* ? means potential                                                                                                                                                                                                | 11                                                                                                                                                                                                                                                                                                                                                                           | /* ? means potential                                                                                                                                                                                                                                                                                                                                                                                           |

| }                                        | 12 ' * deadlock, depending                                                                                                                                                                                             | 12                                                                                                                                                                                                                                                                                                                                                                           | * deadlock, depending                                                                                                                                                                                                                                                                                                                                                                                          |

| <pre>/* × means certain deadlock*/</pre> | 13 * on the if-condition*                                                                                                                                                                                              | / 13                                                                                                                                                                                                                                                                                                                                                                         | * on the if-condition*/                                                                                                                                                                                                                                                                                                                                                                                        |

|                                          | ·                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                |

| (a) group synchronisation                | (b) split-phase sync.                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                              | (c) dynamic membership                                                                                                                                                                                                                                                                                                                                                                                         |

|                                          | <pre>a.advance(); // × c.advance(); } async clocked(b, a) { // t<sub>2</sub> b.advance(); // × a.advance(); } async clocked(c, b) { // t<sub>3</sub> c.advance(); } c.advance(); } /* × means certain deadlock*/</pre> | <pre>a.advance(); // × 2 if (condition) {     c.advance(); 3 b.resume(); } async clocked(b, a) { // t2 5 a.advance(); // ? b.advance(); // × 6 b.advance(); a.advance(); 7 } Basync clocked(c, b) { // t3 9 a.advance(); // ? async clocked(c, b) { // t3 9 a.advance(); c.advance(); 11 /* ? means potential } /* × means certain deadlock*/13 * on the if-condition*</pre> | a.advance(); // × 2 if (condition) { 2<br>c.advance(); 3 b.resume(); 3<br>} b.resume(); 3<br>} async clocked(b, a) { // $t_2$ 5 a.advance(); // ?<br>b.advance(); // × 6 b.advance(); // ?<br>a.advance(); 7 } 7<br>} s b.advance(); 7 } 7<br>} async clocked(c, b) { // $t_3$ 9 a.advance(); // ?<br>b.advance(); 11 /* ? means potential 11<br>} /* ? means certain deadlock*/ 13 * on the if-condition*/ 13 |

Fig. 1. Barrier deadlock Examples 2.1 to 2.3 in X10.

The above example by itself is a global deadlock (the main X10 task, that spawns the three child tasks, implicitly waits for the termination of all spawned tasks). This fragment could, however, constitute a local deadlock as part of a larger system (*e.g.*, by extending the parent task with some continuation), which we formalise in Section 3.2. Dynamic verification of global deadlock is trivial for any system, by simply checking if all (user) tasks are blocked. Many systems implement only global deadlock detection, such as HJ [36], giving a verification that is sound (no false positives) but incomplete (since any non-global deadlock is a false negative).

*Split-phase synchronisation.* Split-phase synchronisation [29, 38] allows a task to perform a barrier synchronisation over two steps, instead of just a single atomic action. A task *initiates* its next synchronisation via a non-blocking background operation, and can *wait* for the synchronisation to conclude, *i.e.*, when all tasks have *initiated* the synchronisation, as a separate operation at a later point. In X10, the initiation operation on clocks is resume, and the wait operation is simply advance (an advance basically includes an implicit resume if not already performed). Split-phase allows a task to concurrently overlap barrier synchronisation with other work, which is useful for, *e.g.*, hiding network latency in distributed programs [9, 11, 74].

EXAMPLE 2.2. In Figure 1 (b), the parent and child tasks synchronise on clocks a and b. Although the two tasks wait on their two clocks in opposite order, there is no deadlock if the condition in the child task evaluates to true as it will initiate the synchronisation on b before waiting on a. Otherwise, a deadlock will occur.

Although split-phase synchronisations are available in every case of Table 1, deadlock detection for split-phase is only supported in UPC [57], facilitated by the restriction to global synchronisations described earlier. In the presence of group synchronisation, a verification would have to consider, in addition to blocking status of tasks and group memberships, the *initiation status* of each task for every synchronisation operation it is involved in. MPI supports split-phase by the immediate MPI\_IBarrier operation, but the deadlock detection in MUST does not take the initiation status of such synchronisations into account [30].

*Dynamic membership.* A barrier restricted to *static* membership does not permit the registration or deregistration of tasks once any member task has commenced execution; in the presence of group

synchronisation, static task groups are typically fixed on barrier creation (*e.g.*, MPI communicators). Conversely, *dynamic* membership allows tasks to be registered and deregistered over the lifetime of a barrier. All of the X10 examples seen so far implicitly feature dynamic membership.

EXAMPLE 2.3. In Figure 1 (c), the child task is dynamically registered to pre-existing clocks a and b, which the parent task is also registered to (in X10, a task may only register a child task to a clock if it itself is registered). If the condition in the parent task evaluates to false, a deadlock arises because the parent task blocks by advance on a, while the child task blocks on b, establishing a circular dependency. Otherwise, the parent dynamically deregisters from b, allowing the child task to successfully terminate, regardless of whether the deregistration occurs before or after the child reaches the advance. On termination, the child implicitly deregisters from its barriers, which in turn allows the parent task to pass its advance.

Static membership simplifies *dynamic* analysis of barrier deadlocks because, for any task waiting on some barrier, the set of candidate tasks which the former task may be waiting for (*i.e.*, its co-members) is a run-time invariant throughout the life-cycle of the barrier. This facilitates WFG-based approaches because the only information required to establish a wait-for dependency from a waiting task to any of its fixed co-member tasks is that the latter has not reached the same barrier. By contrast, dynamic membership means that the set of wait-for candidates can change per phase. A wait-for dependency to some other task *t* first requires confirming that the *t* is indeed a member of the relevant barrier at the point in system execution for which the analysis is being conducted. The difficulty of such checks is compounded when verifying distributed programs, as the query might involve communication between sites to transmit the membership status.

We discuss how Armus supports distributed barriers in Section 6.3. Deadlock detection for distributed barriers is supported by MUST for the static membership barriers of MPI (and non-splitphase synchronisations) [31, 33]; and by UPC, again due to the restriction to global synchronisations. X10 supports distributed barriers as a key language feature, but without any facility for deadlock detection.

# 2.3 Generalised Barrier Synchronisation using Phasers

*Phasers* [8, 62] are a generalisation of barriers. The main feature of phasers is that member tasks may independently progress ahead to a future barrier step (*i.e.*, phase) without synchronising (*i.e.*, waiting for their co-members) on the intermediate steps. Phasers may also support certain usages by non-member tasks.

In this work, we introduce a core language for phaser-coordinated concurrent systems that distils the key functionality of phasers:

- A phaser records the *phase*, an integer  $n \ge 0$ , reached by each member task.

- A *non-blocking* arrv operation on a phaser increments the phase of the calling task. Any member task may thus independently advance up to an arbitrary phase.

- A separate, optional await operation on a phaser blocks the calling task at its current phase until every member task has reached this phase.

- Explicit dynamic membership: tasks are registered and deregistered with a phaser by, and only by, reg and dereg operations.

We develop the deadlock verification of Armus on this basis of this core phaser functionality, which subsumes all of the barrier features summarised in Section 2.2 (Table 1). Armus is thus applicable to all of the languages and libraries discussed there, and to any other barrier system whose functionality can be encoded into these operations.

Listing 2. An asynchronous linear producer-consumer pipeline in a pseudo X10 extended with Armus phaser operations (Example 2.4).

```

// Pre: "ph" is an array of length #num_tasks of new phasers

1

for (i in 0..(num_tasks-1)) {

2

val id = i;

3

val local = ph(id);

4

val pred = ph((id-1+num_tasks)%num_tasks); // Preceding pipeline task's phaser

5

async phased(local, pred) { // Spawned task is registered to these two phasers

6

for (j = 1; j <= num_steps; j++) {</pre>

7

if (id > 0) {

8

arrv(pred)

9

await(pred);

// Await next item from preceding task

10

}

11

step(id, j);

// Consume preceding task's next item and/or..

12

// ..produce next local item as appropriate

13

if (id < num_tasks-1) {</pre>

14

arrv(local);

// Signal item is ready

15

}

16

} } }

17

// Result: every task except #0 has awaited #num_steps on preceding task's phaser,

18

11

every task except #num_tasks-1 has arrived #num_steps on its local phaser

19

```

*Producer-Consumer.* A primary motivation for phasers is to support asynchronous producerconsumer patterns [14, 64] that cannot be expressed using the barrier features discussed in Section 2.2. Such synchronisation patterns occur in programs performing streaming (also known as data-flow) communication among tasks [54, 60, 63]. A typical producer-consumer application using phasers correlates each phase to the production of one item: a producer task arrives at the next phase after producing an item, while consumer tasks arrive and await the phases in sequence. The ability to advance its local phase without awaiting allows the producer to proceed ahead of the consumers, and similarly allows different consumers to progress at different rates. By contrast, a clocked production stream using, *e.g.*, basic cyclic barriers, would require the producer and every consumer to synchronise on every item.

EXAMPLE 2.4. This example is extracted from the LU (Lower-Upper symmetric Gauss-Seidel) benchmark of the NAS Parallel Benchmark (NPB) suite [24] (see Section 7), originally written in Java using condition variables.<sup>10</sup> Listing 2 adapts the example to phasers, which we write in an X10-based pseudo code (for readability) extended with the Armus arrv and await operations.

The child tasks spawned by the async are organised to form a linear pipeline of tasks consuming from one neighbour and producing to the other. Each task is associated with a phaser, stored in an array ph, that counts the number of items it has produced locally. Each task, except the first (0-th), awaits the next phase of the preceding task's phaser (to consume the next available item). Each task, except the last, then asynchronously advances its local phaser (after producing the next item) without waiting. (The details of item production and consumption and any additional work performed by the step method are omitted for brevity.)

ACM Transactions on Programming Languages and Systems, Vol. 1, No. 1, Article 1. Publication date: January 2018.

<sup>&</sup>lt;sup>10</sup>The limited java.util.concurrent.Phaser implementation of phasers supports split-phase synchronisations, but not the fully unrestricted phase advancing required for asynchronous producer-consumer.

Fig. 2. A phaser deadlock.

Incorrect manipulation of task indexes (a typical programming error) in the conditional expressions before and after step can easily give rise to deadlock; *e.g.*, if any task (except the last) does not advance its phaser, or if the first task cyclically waits on the last task's phaser.

The functionality of phasers modelled in Armus subsumes the previously discussed barrier features as follows. *Dynamic membership* is supported by the explicit per-task registration and deregistration operations, which in turn supports *group synchronisation* by allowing an arbitrary subset of tasks to be registered to any given phaser. *Split-phase synchronisation* is subsumed as the special case of phaser usage where, for each member task, an arrv on phaser p is always followed by an await on p before any subsequent arrv on p; *i.e.*, the discrepancy between the phases of the most and least advanced member tasks of a phaser is bounded to a maximum of one.

# 2.4 Dynamic Deadlock Verification for Phasers

We conclude this section by outlining the phaser-based approach of Armus to barrier-deadlock verification. The challenge of deadlock verification for phasers is that tasks may participate in synchronisations on a phaser only at selected phases. Section 2.2 outlined WFG-based deadlock detection for basic barriers (*i.e.*, barriers that require all member tasks must synchronise on every step). Considered simply, such approaches are unsuitable for phasers because they are based on capturing inter-task control flow dependencies at the granularity of *barriers* as synchronisation resources.

| 1 | // t <sub>1</sub>    | 1 | // t <sub>2</sub>   | 1   | // t <sub>3</sub>     |

|---|----------------------|---|---------------------|-----|-----------------------|

| 2 | <pre>arrv(a);</pre>  |   | <pre>arrv(a);</pre> |     | $arrv(a); \leftarrow$ |

|   | <pre>arrv(a);</pre>  |   | <pre>arrv(a);</pre> | 3   | arrv(a);              |

| 4 | <pre>await(a);</pre> |   |                     | 4   | arrv(b);              |

| 5 | arrv(b);             | 5 | await(b);           | ← 5 |                       |

| 6 | await(b);            | 6 |                     | 6   |                       |

|   |                      |   |                     |     |                       |

In the above *deadlock-free* phaser code, all three tasks,  $t_1$ ,  $t_2$  and  $t_3$ , are registered to both phasers, a and b, and execution has reach the state indicated in each task:  $t_1$  and  $t_2$  are blocked, but not  $t_3$ . Naive application of a basic WFG-based approach (*i.e.*, building task-to-task wait-for dependencies by treating *phasers* as standard cyclic barriers) to this system would result in a *false positive*: a cycle arises because  $t_1$  is blocked on a which  $t_2$  is a member of, and  $t_2$  is blocked on b which  $t_1$  is a member of. The problem is that the construction of this false cycle involving two tasks and two phasers is insensitive to the fact that there are actually three *phases* in play.

#### Tiago Cogumbreiro, Raymond Hu, Francisco Martins, and Nobuko Yoshida

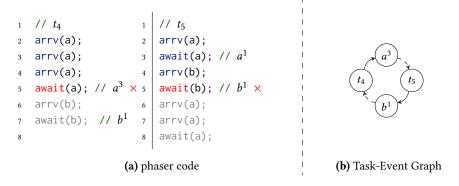

On the other hand, bad asynchronous phase advancing patterns can easily give rise to deadlocks, as illustrated in Figure 2 (a). Both  $t_4$  and  $t_5$  will await on a, then await on b. However,  $t_5$  blocks on its first phase of b after arriving at its first phase on a, but without arriving at its second or third phases on a—which  $t_4$  requires in order to progress to the arrive at its first phase on b.

*Armus: Task-Event Graphs.* Our approach is based on modelling the concurrency constraints of phaser systems at the granularity of *phases.* The intuition is that the operations performed by tasks on any given phaser induces an ordered series of *phase synchronisation events* on that phaser. (We may refer to phase synchronisation events as *phase events*, or simply *events*.) More specifically, a task may be related to a phase event because it is *waiting on* the event, *i.e.*, to participate in the synchronisation on this phase; or because the event is being *impeded by* the task, *i.e.*, the synchronisation event cannot occur because the task has not reached this phase.

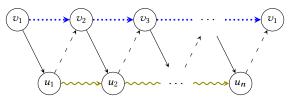

Armus introduces a *Task-Event Graph* (TEG) model that can be considered as adapting traditional Task-Resource Graph models [61] to phaser systems by treating each phase event as a distinct temporal synchronisation resource. The resulting model is a bipartite graph of task and event nodes with the following key characteristics:

- A TEG models separate task wait-on event, and event impede-by task, relations.

- The impede-by relation incorporates a notion of *phase-transitivity* induced by event ordering: an event is inherently impeded by a task, if the task is associated with another event at any *earlier* phase on the same phaser.

As a preliminary example, Figure 2 (b) depicts the TEG for the deadlock situation of Figure 2 (a). The notation, *e.g.*,  $a^3$  means phase 3 on phaser *a*. The solid edges  $(t_4, a^3)$  and  $(t_5, b^1)$  are given by the wait-on relation, and  $(a^3, t_5)$  and the dashed edges  $(b^1, t_4)$  by the impeded-by relation. We can explain the  $(a^3, t_5)$  edge by because (i) there is a task waiting on  $a^3$  (in this case  $t_4$ ), and (ii) and task  $t_5$  is waiting on  $b^1$  while having only reached a phase that precedes  $a^3$  (in this case  $t_5$  reached  $a^1$ ).

In Sections 3 to 5, we formalise the Armus phaser language and dynamic deadlock verification methodology, and show that the verification is sound and complete. Section 6 discusses our implementations of Armus for X10 and Java.

# 3 A CORE PHASER-BASED LANGUAGE FOR GENERAL BARRIER SYNCHRONISATIONS

This section introduces the syntax and semantics of a core concurrent language with phasers, which we refer to as BRENNER. The language is designed to express abstractions of concurrent, imperative barrier programs, sufficient to formalise our deadlock verification and show the verification properties. The main purposes of the formalism are to define the information required of a phaser system to characterise a deadlock, namely the state of the data structure underlying each phaser and the set of blocked tasks, and to model how the phaser operations act on this information. Since the run-time verification approach of Armus works by sampling the state of phasers and blocked tasks during program execution, the correctness of the deadlock analysis is independent of control flow mechanisms. Language constructs that do not directly affect barrier synchronisation are omitted, such as local data operations, or simplified, *e.g.*, looping constructs are abstracted as a non-deterministic loop statement.

#### 3.1 BRENNER: A Core Phaser-Based Language

*Phasers.* We first formalise the core functionality of phasers. Let *P* denote a *phaser* that maps *task names*  $t, t', \ldots \in \mathcal{T}$  to *local phases*, ranging over the natural numbers,  $n \in \mathcal{N}$ . Predicate await(*P*, *n*), used by tasks to observe a phase event, holds iff every member of the phaser has a local phase of at

# Phasers

$$\frac{\exists t': P(t') \leq n}{P \stackrel{\text{reg}(t,n)}{\longrightarrow} P \uplus \{t:n\}} \quad \text{[add]} \quad M \stackrel{p:=P}{\longrightarrow} M \uplus \{p:P\} \quad \text{[add-p]}$$

$$P \uplus \{t:n\} \stackrel{\text{dereg}(t)}{\longrightarrow} P \quad \text{[drop]} \quad \frac{P \stackrel{\phi}{\longrightarrow} P'}{M \uplus \{p:P\} \stackrel{p.\phi}{\longrightarrow} M \uplus \{p:P'\}} \quad \text{[upd]}$$

$$P \uplus \{t:n\} \stackrel{\text{arrv}(t)}{\longrightarrow} P \uplus \{t:n+1\} \quad \text{[adv]} \quad M \eqqcolon \{p:P\} \stackrel{p.\phi}{\longrightarrow} M \uplus \{p:P'\}$$

Instructions

$$skip; s \rightarrow s$$

[skip]

$$\frac{s' = c_1; ..; c_n; \text{end}}{\text{loop } s'; s \to c_1; ..; c_n; (\text{loop } s'; s)}$$

[i-loop]

$$loop s'; s \to s \qquad [e-loop]$$

States

$$\frac{t^{\prime\prime} \notin \mathrm{fv}(s)}{(M, T \uplus \{t^{\prime} \colon t = \mathsf{newTid}(); s\}) \to (M, T \uplus \{t^{\prime} \colon s[t^{\prime\prime}/t]\} \uplus \{t^{\prime\prime} \colon \mathsf{end}\})}$$

[new-t]

$$(M, T \uplus \{t': \mathsf{fork}(t) \ s; s'\} \uplus \{t: \mathsf{end}\}) \to (M, T \uplus \{t': s'\} \uplus \{t: s\})$$

[fork]

$$\frac{M \xrightarrow{q := P} M' \quad P = \{t : 0\} \quad q \notin fv(s)}{(M, T \uplus \{t : p = \mathsf{newPhaser}(); s\}) \to (M', T \uplus \{t : s[q/p]\})}$$

[new-p]

$$\frac{M(p)(t') = n \qquad M \xrightarrow{p.\operatorname{reg}(t,n)} M'}{(M,T \uplus \{t': \operatorname{reg}(t,p);s\}) \longrightarrow (M',T \uplus \{t':s\})}$$

[reg]

$$\frac{M \xrightarrow{p.\operatorname{dereg}(t)} M'}{(M, T \uplus \{t: \operatorname{dereg}(p); s\}) \to (M', T \uplus \{t: s\})}$$

[dereg]

$$\frac{M \xrightarrow{p.\operatorname{arrv}(t)} M'}{(M, T \uplus \{t: \operatorname{arrv}(p); s\}) \to (M', T \uplus \{t: s\})}$$

[arrv]

$$\frac{M(p) = P \quad \text{await}(P, n)}{(M, T \uplus \{t: \text{await}(p, n); s\}) \rightarrow (M, T \uplus \{t: s\})}$$

[await-n]

$$\frac{M(p)(t) = n \qquad (M, T \uplus \{t: \operatorname{await}(p, n); s\}) \to (M, T')}{(M, T \uplus \{t: \operatorname{await}(p); s\}) \to (M, T')}$$

[await]

$$\frac{s \to s'}{(M, T \uplus \{t:s\}) \to (M, T \uplus \{t:s'\})}$$

[c-flow]

Fig. 3. Operational semantics of BRENNER.

Tiago Cogumbreiro, Raymond Hu, Francisco Martins, and Nobuko Yoshida

Listing 3. The BRENNER representation of the X10 example in Listing 1.

```

// Body of the main (parent) task t0:

1

p_c = \text{newPhaser()}; // X10 clock (cyclic barrier), parent task implicitly registered

p_f = \text{newPhaser()}; // X10 finish (join barrier), parent task implicitly registered

3

loop

4

t = \text{newTid}();

// Child task

5

reg(p<sub>f</sub>, t); reg(p<sub>c</sub>, t); // X10: (implicit) finish reg, (explicit) clock reg

6

fork(t)

7

loop

8

skip;

9

arrv(p_c); await(p_c); // clock advance ×

10

11

skip;

\operatorname{arrv}(p_c); \operatorname{await}(p_c); // clock advance

12

end:

13

dereg(p_c); // X10 task termination..

14

dereg(p_f); // ...deregisters the task from all barriers

15

end;

16

end;

17

arrv(p_f); await(p_f); // finish synchronisation ×

18

// finish statement exit

dereg(p_f);

19

end

20

```

least n:

await

$$(P, n) \stackrel{\text{def}}{=} \forall t \in \text{dom}(P) \colon P(t) \ge n$$

For a map *X*, we write dom(*X*) for the domain of *X*, and img(*X*) for the image of *X*. When  $X \cap Y = \emptyset$  for some map *Y*, we write  $X \uplus Y$  for the disjoint union of *X* and *Y*.

Three atomic operations  $\phi$  mutate a phaser, as defined by "Phasers" in Figure 3. reg(t, n) registers a task named t to phaser P with initial phase n, provided that the task is not already a member. dereg(t) removes the calling task t from the membership of P. arrv(t) increments the local phase of t in P.

Let a *phaser map* M be a map from phasers names  $p, p', \ldots \in \mathcal{P}$  to phasers, used to record all the phasers in a system. There are two operators o on phaser maps: p := P names the new phaser P with a global name p, and  $p.\phi$  updates the phaser named p according to  $\phi$ .

*Syntax.* BRENNER abstracts a user-level program as a sequence *s* of instructions *c*, generated by the grammar:

Operational semantics. The reduction of BRENNER terms is defined by "Instructions" and "States" in Figure 3. A task map T maps task names  $t_i$  to instruction sequences  $s_i$ , representing the current state of the running tasks. A system state, or simply state, is a pair S::=(M, T).

We explain the syntax and operational semantics through Listing 3, which gives the BRENNER representation of the X10 example from Listing 1. Spawning a new task comprises two instructions:

ACM Transactions on Programming Languages and Systems, Vol. 1, No. 1, Article 1. Publication date: January 2018.

create a fresh task name bound as t by newTid (*e.g.*, Line 5), and fork a task with this name to perform instruction sequence s by fork(t) s (*e.g.*, Lines 7 to 16). The former adds a dummy (non-executable) task as a placeholder in the task map, to reserve the name t until the latter occurs.

Regarding task membership, newPhaser creates a phaser and registers the current task at phase zero. Rule [reg], with reg(p, t), lets some task t' register a new task t with phaser p. Task t' must be registered with p, and t inherits the phase of t';<sup>11</sup> rule [add] enforces that t is not already a member of p. Additionally, condition  $P(t') \leq n$  guarantees that there is some task, trivially the caller t', that is registered on phase n, so as to ensure that phaser synchronisation is deterministic—observing a phase must be a stable property; otherwise, there would be no way to know when synchronisation happened, as new participants could be introduced in past phases. Operation dereg(p) deregisters the current task from phaser p. In the example, the parent task creates a phaser representing the X10 join barrier  $p_f$  in Line 3, and registers child tasks t to  $p_f$  in Line 6, which deregister from  $p_f$  to signal task termination in Line 15.

For synchronisation,  $\operatorname{arrv}(p)$  is the non-blocking operation for the current task to arrive at its next local phase, and  $\operatorname{await}(p)$  blocks the current task t until  $\operatorname{await}(P, n)$ , where n is the local phase of t on P, the phaser named p. In the inner loop of the example (Lines 10 to 12), each child task advances its phase and then awaits the others to do the same. The variant await(p, n) takes n as an explicit argument and does not require t to be registered to p, which captures use cases such as the *wait-only* phaser "registration" mode of HJ [62].<sup>12</sup>

Lastly, the structural rule for control flow is standard. In BRENNER, local data operations are abstracted as skip, and the non-deterministic loop, which unfolds its body an arbitrary number of times (possibly zero), is used to subsume the control flow of standard conditional branches, while-loops and so on.

With respect to the dynamic deadlock verification, rules [await] and [await-n] are used to define the notion of blocked tasks, in order to characterise deadlocked states (Section 3.2) and establish the results in Section 5. Second, the operational semantics as whole serves as a specification of how phaser system state should be maintained by an implementation of Armus verification (or conversely, a specification of the phaser systems to which an implementation of Armus applies), as we discuss for X10 and Java in Section 6.2.

# 3.2 Phaser Deadlocks

A *phase event e*, or simply *event*, is a pair (p, n), which may be written as  $p^n$ . The ordering of phase events on a phaser is given by the *precedes* relation on events, e < e':

$$\frac{n < m}{(p,n) < (p,m)}$$

Given a state S = (M, T), a task  $t \in T$  and an event  $e = (p, n), p \in \text{dom}(M)$ , we define:

- *t* is *waiting on* on *e*, notation *t* WAIT-ON<sub>S</sub> *e*, iff *t* is awaiting phase *n* on *p*. That is, there exists *s* such that T(t) = await(p, n); *s*, or T(t) = await(p); *s* and M(p)(t) = n. In such cases, we also simply say *t* is *awaiting*.

- *t* is associated with *e*, notation *t* ASSOC<sub>S</sub> *e*, iff M(p)(t) = n.

- *e* is *impeded by t*, notation *e* IMPEDE-BY<sub>S</sub> *t*, iff *t* ASSOC<sub>S</sub> *e'* such that e' < e and there exists a task *t'* where *t'* WAIT-ON<sub>S</sub> *e*. In such a case, we also simply say *e* is *impeded*.

Given an *S*, we will write simply WAIT-ON<sub>S</sub> to denote the set of all (t, e) pairs such that t WAIT-ON<sub>S</sub> e; similarly for IMPEDE-BY<sub>S</sub>.

<sup>&</sup>lt;sup>11</sup>Phase inheritance subsumes the X10 notion of child tasks inheriting the "initiation status" of split-phase synchronisations. <sup>12</sup> In HJ, *wait-only* registration is a special case where the task is implicitly assigned a local phase of  $\infty$  and is not permitted to arrive on the phaser. In Armus, this is modelled as allowing non-member tasks to await (but not arrive) on a phaser.

An *e* impeded by *t* relationship, where e = (p, n), signifies that *t* has a strictly earlier local phase on *p* than *n*, and is thus required to perform some action, namely either at least one  $\operatorname{arrv}(p)$  or a  $\operatorname{dereg}(p)$ , before *e* can be successfully observed by any awaiting task. Moreover, there is at least one such task *t'* awaiting *e*, which ensures that the impede-by relation is finite. Note that, while a task may be waiting on at most one event, an event may be impeded by multiple tasks.

Unlike the wait-for relation in WFG-oriented approaches, neither wait-on nor impede-by inherently capture any notion of a task being stuck in of themselves. Instead, we naturally characterise phaser deadlock based on mutual dependencies between the two relations as follows. We define *deadlocked states* (*i.e., local deadlock*, as discussed in Section 2.2) based on *totally deadlocked states* (global deadlock). A totally deadlocked state occurs when every task is waiting-on some event and the event is impeded by some task.

Definition 3.1 (Totally deadlocked state). A state (M, T) is totally deadlocked iff  $T \neq \emptyset$  and  $\forall t \in$ dom(T).  $\exists e \in$ dom $(M) \times N$ . $(t \text{ wAIT-ON}_S e \land e \text{ is impeded})$ .

A totally deadlocked state extended with tasks that are not awaiting impeded events is considered as simply *deadlocked*, as the system may still potentially progress by the reduction of these additional tasks.

Definition 3.2 (Deadlocked state). A state  $S = (M, T \uplus T')$  is deadlocked on T iff the state (M, T) is totally deadlocked. In such a case, we also simply say S is deadlocked.

The notion of local deadlocks is crucial for applications that may never terminate (typical examples being operating systems and persistent network services), and practically important for systems that may simply be long running.

# 4 DYNAMIC DEADLOCK VERIFICATION FOR PHASERS

This section first defines the construction of Task-Event Graphs (TEGs) from BRENNER system states. Second, by starting from a more general model oriented to TEGs (as opposed to a directly WFGoriented approach), we are able to recover smaller but equivalent, with respect to the verification properties (Section 5), representations as optimisations. These are the WFG, and the counterpart notion of State Graph (SG).

# 4.1 Task-Event Graphs

*Background.* A *Task-Resource Graph* (TRG) [61], also known as *Transaction-Resource Graph*, is a bipartite directed graph used to model concurrency constraints between tasks and resources. We adapt this term as *Task-Event Graph* (TEG) in Armus, since we model the concurrency constraints arising from tasks observing transient phase events by collective synchronisation operations, as opposed to individual acquisition and release actions on "concrete" resources.

Holt generalised TRGs to *General Resource Graphs* (GRG) [35], by augmenting resource-nodes with the number of available resources. Unlike TEGs, a GRG cycle does *not* necessarily imply deadlock. The GRG must first be transformed a finite number of steps to identify a potential deadlock. Non-bipartite directed graphs of tasks and synchronisation mechanisms have also been used to detect lock-based deadlocks [52].

Coffman *et al.* introduced the *State Graph* (SG) [12] to model concurrency constraints directly between synchronisation mechanisms. State-of-the-art on identifying potential lock-based deadlocks includes approaches based on SGs [7, 23, 58], where SGs also known as Lock-Order Graphs and Lock-Dependency Graphs. SGs have also been used to infer deadlock-free contracts for concurrency libraries [21].

Knapp introduced the *Wait-For Graph* (WFGs) [40] to model concurrency constraints directly between tasks. As discussed earlier, variations of WFGs are used in the state-of-the-art on deadlock detection for distributed message passing and (static membership) barriers [34, 37].

Basic concepts from graph theory. A (directed) graph G is a pair (V, A) comprising a nonempty finite set of vertices V, ranged over by v, u, and a finite set of arcs A, ranged over by a, b, c, where an arc a is a pair (v, u) with  $v, u \in V$ . An arc (v, u) is directed from its head v to its tail u. We write  $a \in G$  to mean G = (V, A) and  $a \in A$ . Graph (U, B) is a subgraph of graph (V, A) iff  $U \subseteq V$ and  $B \subseteq A$ .

A walk w on (V, A) is a (possibly empty) sequence  $a_1 \cdots a_n$  (also written  $a_{1..n}$ ) of arcs in A such that, for all i < n,  $a_i = (v_i, v_{i+1})$  and  $a_{i+1} = (v_{i+1}, v_{i+2})$ . We write  $\epsilon$  to denote the walk of length zero and a: w to prepend edge a to walk w. For instance, walk  $(v_1, v_2): (v_2, v_3): \epsilon$  is an alternative notation for walk  $(v_1, v_2) \cdot (v_2, v_3)$ .

We write  $a \in w$  to mean  $w = a_{1..n}$ , where there exists  $i \in \{1, ..., n\}$  and  $a = a_i$ ; and  $v \in w$  to mean there exists  $(v_1, v_2) \in w$  and  $v \in \{v_1, v_2\}$ . We have that  $v_2 \in (v_1, v_2) \cdot (v_2, v_3)$  and that  $(v_2, v_3) \in (v_1, v_2) \cdot (v_2, v_3)$ , yet  $v_4 \notin (v_1, v_2) \cdot (v_2, v_3)$  and that  $(v_5, v_5) \notin (v_1, v_2) \cdot (v_2, v_3)$ .

We may write a walk by its constituent vertices, *i.e.*,  $(v_1, v_2) \cdot (v_2, v_3) \cdots (v_{n-1}, v_n)$  abbreviated as  $v_1 \cdot v_2 \cdots v_{n-1} \cdot v_n$ . For instance, walk  $v_1 \cdot v_2 \cdot v_3$  is an alternative notation for walk  $(v_1, v_2) \cdot (v_2, v_3)$ .

We may also simply refer to a walk by its first and last vertices, *i.e.*, a  $v_1$ - $v_n$  walk means a nonempty walk  $v_1 \cdots v_n$ . Given a walk  $w = a_1 \cdots a_n$  such that  $n \ge 1$ , we have that  $a_n$  is the last arc of walk *w*. A *cycle* is a v-v walk—note that cycles are nonempty walks.

A bipartite graph G = (V, U, A) is a graph  $(V \cup U, A)$  where V and U are disjoint and, for all  $a \in A$ , a = (v, u) or a = (u, v) with  $v \in V$  and  $u \in U$ .

*Task-Event Graphs.* A Task-Event Graph (TEG) is a bipartite graph where the two disjoint sets of vertices are task names  $t \in \mathcal{T}$  and events  $e \in \mathcal{P} \times \mathcal{N}$ . A TEG thus has two kinds of arcs: *wait-on* arcs (t, e) directed from a task t to an event e, and *impede-by* arcs (e, t) from an event e to a task t.